集成電路產(chǎn)業(yè)鏈 設(shè)計環(huán)節(jié)的核心技術(shù)與流程

集成電路(Integrated Circuit,IC)是現(xiàn)代信息技術(shù)的基石,其產(chǎn)業(yè)鏈可分為設(shè)計、制造、封測三大核心環(huán)節(jié),以及上游的材料、設(shè)備等支撐產(chǎn)業(yè)。其中,設(shè)計環(huán)節(jié)作為產(chǎn)業(yè)鏈的起點,承擔(dān)著將創(chuàng)新理念轉(zhuǎn)化為具體電路圖與規(guī)格的關(guān)鍵任務(wù),是技術(shù)附加值最高、智力最密集的部分。

一、設(shè)計環(huán)節(jié)的定義與重要性

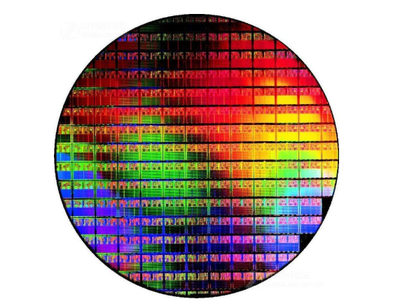

集成電路設(shè)計,是指根據(jù)系統(tǒng)需求,利用電子設(shè)計自動化(EDA)工具,在芯片上規(guī)劃、設(shè)計和驗證數(shù)十億個晶體管及其他元件的布局與連接關(guān)系,最終形成可供制造的光罩(掩膜版)圖形數(shù)據(jù)(GDSII文件)。設(shè)計環(huán)節(jié)直接決定了芯片的功能、性能、功耗(PPA,即Performance、Power、Area)和成本,是整個產(chǎn)業(yè)鏈的“大腦”與“靈魂”。一個成功的芯片設(shè)計,往往需要深厚的系統(tǒng)知識、電路理論、工藝理解和算法功底。

二、主要設(shè)計流程與核心技術(shù)

典型的芯片設(shè)計是一個分層迭代的復(fù)雜過程,主要包含以下階段:

- 系統(tǒng)架構(gòu)與規(guī)格定義:基于應(yīng)用場景(如智能手機、汽車、AI服務(wù)器),明確芯片的功能、性能指標(biāo)、功耗預(yù)算、接口協(xié)議和成本目標(biāo)。這是設(shè)計的“藍圖”階段。

- 前端設(shè)計(邏輯設(shè)計):

- 寄存器傳輸級(RTL)設(shè)計:使用硬件描述語言(如Verilog、VHDL)將架構(gòu)轉(zhuǎn)化為可綜合的寄存器級代碼,描述數(shù)字電路的數(shù)據(jù)流與控制邏輯。

- 功能驗證:通過仿真、形式驗證等方法,確保RTL代碼的功能與規(guī)格定義完全一致。驗證工作量通常占設(shè)計總工作量的70%以上。

- 邏輯綜合:利用EDA工具,將RTL代碼映射到特定工藝庫的標(biāo)準(zhǔn)單元(如與門、或門、觸發(fā)器等),生成門級網(wǎng)表。此階段會進行初步的時序和功耗分析。

- 后端設(shè)計(物理設(shè)計):

- 布圖規(guī)劃:確定芯片核心區(qū)域、模塊擺放、電源網(wǎng)絡(luò)和I/O引腳位置。

- 布局與布線:將門級網(wǎng)表中的單元精確放置在芯片上,并完成所有單元之間的金屬連線。這是決定芯片面積、時序和功耗的關(guān)鍵步驟。

- 時序收斂與物理驗證:通過靜態(tài)時序分析(STA)確保所有信號路徑滿足時序要求;進行設(shè)計規(guī)則檢查(DRC)和版圖與原理圖一致性檢查(LVS),確保版圖符合制造工藝規(guī)則且與網(wǎng)表一致。

- 簽核:完成最終的時序、功耗、信號完整性、可靠性等分析,生成最終的GDSII版圖文件交付給晶圓廠。

三、設(shè)計環(huán)節(jié)的關(guān)鍵參與者與商業(yè)模式

- 設(shè)計公司類型:

- 無晶圓廠設(shè)計公司:專注于設(shè)計,將制造、封測外包給專業(yè)代工廠(如臺積電、中芯國際)和封測廠。代表企業(yè)有高通、英偉達、AMD、華為海思等。

- 集成器件制造商:擁有設(shè)計與制造能力,如英特爾、三星。

- 設(shè)計服務(wù)與IP供應(yīng)商:提供設(shè)計服務(wù)、驗證服務(wù)或出售預(yù)先設(shè)計好的、可復(fù)用的功能模塊(IP核,如ARM的CPU核、Synopsys的接口IP)。

- 核心支撐:EDA工具與IP核:

- EDA工具:是設(shè)計的“畫筆”與“腳手架”,覆蓋從設(shè)計到驗證的全流程。全球市場主要由新思科技(Synopsys)、楷登電子(Cadence)和西門子EDA(原Mentor Graphics)三大巨頭壟斷。

- IP核:極大地提高了設(shè)計效率和可靠性,是現(xiàn)代SoC(片上系統(tǒng))設(shè)計的基石。

四、面臨的挑戰(zhàn)與發(fā)展趨勢

- 挑戰(zhàn):隨著工藝節(jié)點進入納米尺度(如3nm、2nm),設(shè)計面臨物理效應(yīng)復(fù)雜(如量子隧穿)、功耗墻、設(shè)計成本指數(shù)級上升(先進節(jié)點芯片設(shè)計成本可達數(shù)億美元)、人才短缺等嚴峻挑戰(zhàn)。

- 趨勢:

- 異構(gòu)集成與Chiplet:通過將不同工藝、功能的芯粒(Chiplet)進行先進封裝集成,以平衡性能、成本與開發(fā)周期。

- AI賦能設(shè)計:利用人工智能/機器學(xué)習(xí)優(yōu)化布局布線、加速驗證和設(shè)計空間探索。

- 系統(tǒng)級協(xié)同優(yōu)化:從傳統(tǒng)的芯片設(shè)計轉(zhuǎn)向芯片-封裝-板級-系統(tǒng)的全棧協(xié)同設(shè)計與優(yōu)化。

- 新興領(lǐng)域驅(qū)動:高性能計算、人工智能、汽車電子、物聯(lián)網(wǎng)等對芯片的定制化、高能效需求,催生了更多專用芯片(ASIC)和領(lǐng)域?qū)S眉軜?gòu)(DSA)。

###

集成電路設(shè)計環(huán)節(jié)是連接市場需求與物理實現(xiàn)的橋梁,是知識、工具和創(chuàng)造力高度融合的領(lǐng)域。它不僅推動著摩爾定律的延續(xù),更在“后摩爾時代”通過架構(gòu)與系統(tǒng)創(chuàng)新,持續(xù)引領(lǐng)信息產(chǎn)業(yè)的變革。對于我國而言,突破EDA工具、高端IP核等關(guān)鍵環(huán)節(jié)的技術(shù)壁壘,構(gòu)建安全可控的設(shè)計生態(tài),是提升集成電路產(chǎn)業(yè)核心競爭力的重中之重。

如若轉(zhuǎn)載,請注明出處:http://www.b265.cn/product/64.html

更新時間:2026-04-16 12:43:33